【48812】Cadence Virtuoso规划的一个反相器LVS验证事例

一个地图规划好今后,发生的过错可能是多连了一根铝线形成的Short,或者是少连了几根铝线形成的Open,这样的初级过错对来说都是丧命的,因而修改好的地图要经过LVS(Layout Versus Schemat)与原理图进行核对验证。然后再进行惯例的DRC(Design Rule Check)。

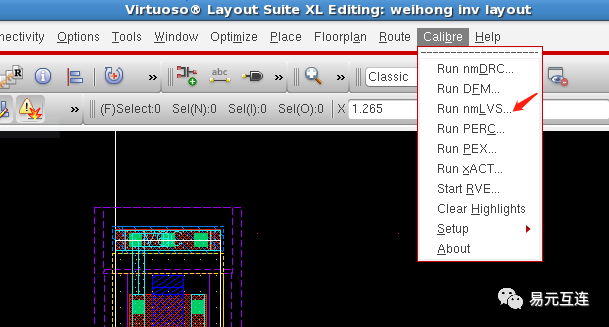

Vertuoso的地图一定要经过的Calibre来进行LVS验证和DRC查看(是不是很美妙?用Cadence公司软件规划的地图,却需求经过Mentor公司的东西来做验证,原因我也想不通,那就别想了,往下持续看吧!),走运的是Calibre现已被集成到Vertuoso软件中了,咱们不需求再翻开别的一个软件界面来操作了。

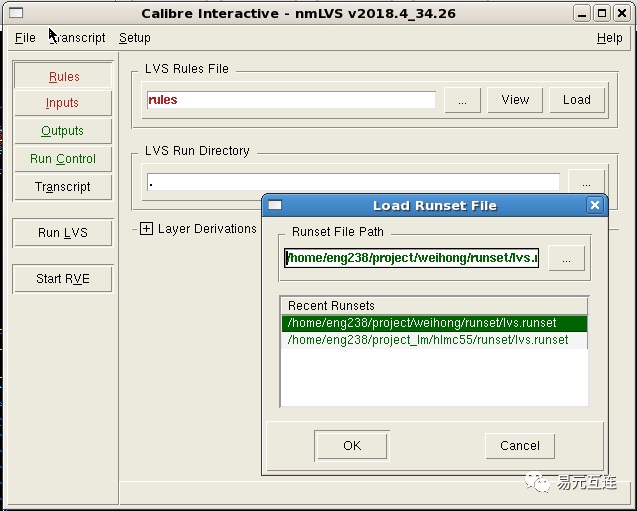

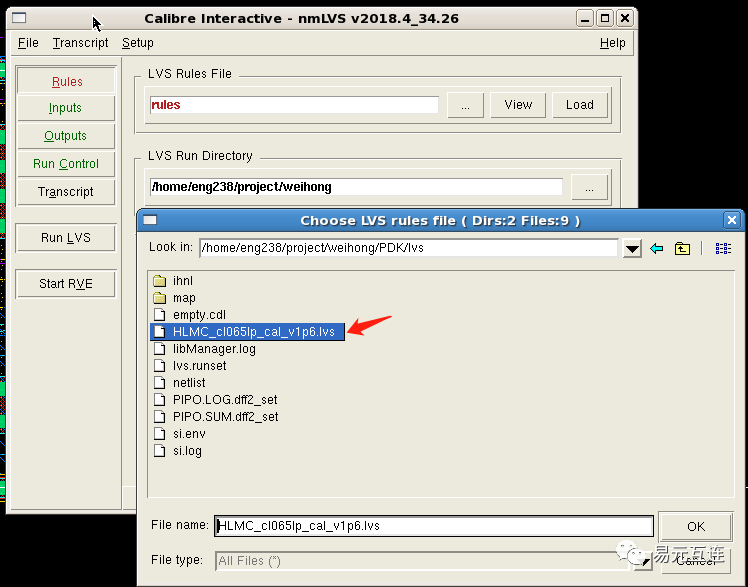

2.然后弹出一个LVS,看到内部还嵌入了一个 LoadRunset File文件的对话框,这个是让咱们终究挑选保存好的runset文件的,由于要从0开端,就点击cancel”;

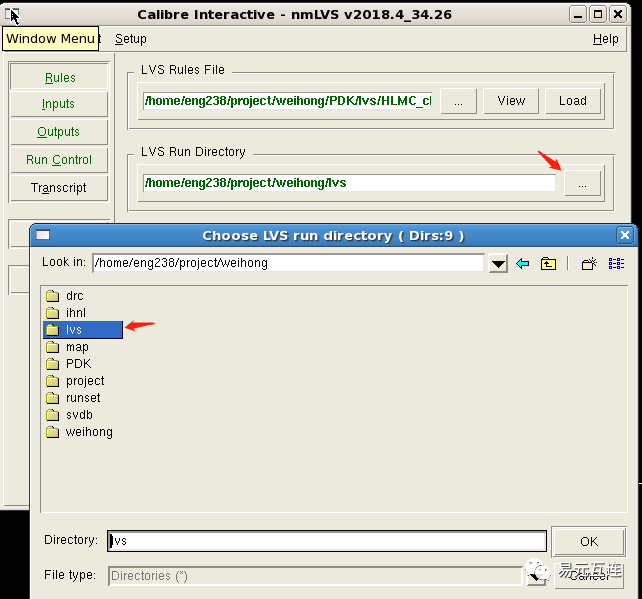

4、在project下新建一个lvs的文件夹(Linix怎么新建文件夹,是linix的操作,不属于本章内容,你们可以自行找材料脑补下),然后LVS Run Dire-

5、点击左边Input的标签,选中右侧下的Netlist标签,可以正常的看到Spice Files有一个默许的inv.calibre文件,这个是反相器的Netlist文件,需求增加下其他规矩文件,一起选中“Export from layout viewer”(第一次一般色彩不会变赤色,需求空运转下LVS后,才干变红);

点击Spice Files右侧按钮,挑选PDK文件包内的empty.cdl文件后,点击“增加”和“OK”;

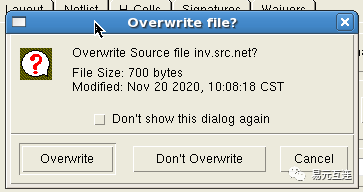

8.然后就点击左边的Run LVS标签,进行LVS验证了,有极大几率会呈现要掩盖前次验证成果的承认对话框,直接挑选Overwrite掩盖就好了;

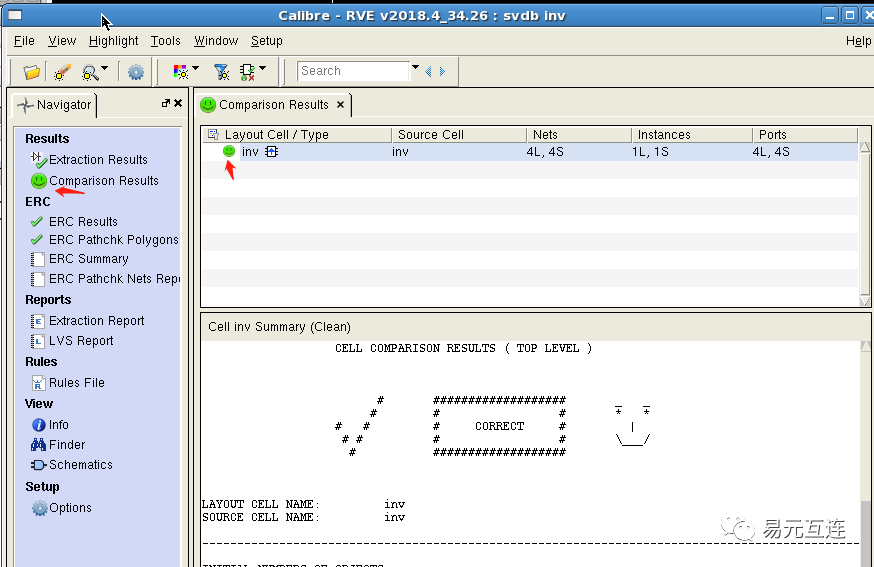

9、最终成果呈现了一个绿色的笑脸,这个阐明验证是OK的,假设渐渐的呈现黑脸,便是有过错的。

5.1.。。。。。太不爽了,成果windows版的还不会用。。。被教师激烈的轻视了。。。。成果他也不会,我就呵呵了。。。要完结悉数规划,包含地图设

衔接,完成”双限“,仿真时没什么问题,焊接后发现当黑色箭头处输出0的时分,赤色箭头输出1.1伏左右,但与

的详细材料阐明 /

查看 /

和静态寄存器的电路规划以及功用仿真,合适入门。还做了地图规划,可是自己对原理不是不清楚,在此就不记录了。

进行根本的电路规划 /

过程 /

搭载AMD锐龙嵌入式7000的研华AIMB-723,主动光学检测AOI解决方案

【GD32H757Z海棠派开发板使用手册】第四讲 FMC-片内Flash擦写读试验

AMD Versal AI Edge自适应核算加快渠道之体会ARM,裸机输出(7)

【Vision Board创客营连载体会】RT-Thread 之wifi连网

- 上一篇:公司开除员工的“100个理由”

- 下一篇:【48812】我国PEX管数据监测陈述